Intel Rialto Bridge é anunciada como próxima GPU da marca para servidores

Por Renan da Silva Dores • Editado por Wallace Moté |

Durante conferência na ISC 2022, feira dedicada à Computação de Alta Performance (HPC), a Intel oficializou a GPU para servidores Rialto Bridge, divulgando os primeiros detalhes da solução. Sucessora da Ponte Vecchio, estreia da empresa no segmento, a nova solução traz mudanças significativas na arquitetura e promete ser a transição ideal para Falcon Shores, a primeira geração do que a companhia chama de XPU.

- Intel e Samsung teriam discutido possível cooperação na produção de chips

- Nvidia anuncia servidores com CPU Grace para streaming de jogos, IA e mais

Intel Rialto Bridge é próxima GPU da marca para servidores

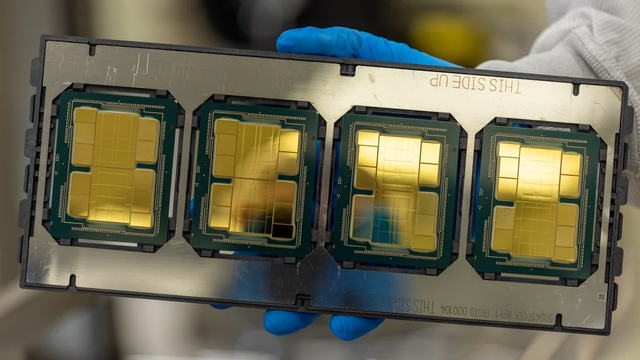

A Intel se absteve de divulgar muitos detalhes técnicos sobre a Rialto Bridge, mas com as informações divulgadas e as fotos publicadas do componente, é possível saber algumas das principais mudanças que a próxima aceleradora de HPC da marca oferecerá. A primeira delas é o aumento do número máximo de Xe Cores, que sobe de 128 para 160.

Observar a imagem da GPU mostra como a Intel reorganizou as estruturas de computação — os 128 Xe Cores da Ponte Vecchio eram distribuídos em 16 chiplets com 8 Xe Cores cada, enquanto a Rialto Bridge utilizará apenas 8 chiplets mais longos, que parecem embarcar 20 Xe Cores cada, com comunicação estabelecida pela memória cache Rambo de alta velocidade da companhia.

Vale destacar que os números ainda são especulativos, já que a gigante não detalhou a arquitetura utilizada. Nem mesmo se sabe se a microarquitetura Xe-HPC será mantida, ou se essa seria uma sucessora, possivelmente chamada Xe²-HPC, mas está bastante claro que a quantidade de chiplets usados para compor o acelerador foi reduzida, indo de 47 para o que parece ser um total de 31.

Também está confirmado que novas litografias serão usadas para a fabricação dos chiplets, mas novamente não foram divulgados quais seriam os processos. Considerando a janela de estreia prevista para 2023, pode-se especular o Intel 4, de 7 nm, e o N5 e N4 da TSMC, de 5 nm e 4 nm respectivamente, como possíveis candidatos.

Ainda segundo a Intel, a Rialto Bridge deve entregar performance 30% superior em cenários reais frente à Ponte Vecchio, salto respeitável considerando a janela de lançamento de um ano entre as duas, ainda que a maior parte dos ganhos deve ser resultado do aumento de 25% na quantidade de núcleos.

A largura de banda deve aumentar, apesar de não estar claro se isso se refere a um novo barramento, como o PCIe 6.0, ou uma geração mais recente da Xe Link, que estabelece a comunicação entre a CPU e múltiplos aceleradores, como também o consumo. Utilizando o novo soquete OAM 2.0 (Open Accelerator Module 2.0), ainda mantido em sigilo no momento, cada Rialto Bridge atingiria TGP de 800 W.

O valor, um dos mais altos entre GPUs para servidores, é um dos fatores que estariam incentivando companhias a substituir a refrigeração a ar por resfriamento líquido, apoiado por lançamentos como a Nvidia A100 e a H100 preparados para water cooling. Mais detalhes da Intel Rialto Bridge devem ser divulgados no decorrer do ano, conforme 2023 se aproxima.

Intel Falcon Shores ganha novos detalhes

A gigante de Santa Clara também aproveitou a oportunidade para divulgar mais detalhes sobre o Intel Falcon Shores, a primeira XPU da companhia. O componente pretende unir as CPUs Xeon e as GPUs Xe-HPC em um único soquete, utilizando técnicas avançadas de empilhamento de chiplets, chamados pela marca de tiles.

A ideia é essencialmente aprimorar o desempenho e tornar os aceleradores mais escaláveis e customizáveis para diferentes servidores, algo que a AMD também estaria planejando fazer com uma abordagem parecida através das APUs de exaescala da família Instinct MI300, segundo rumores.

Anunciado em fevereiro, o Falcon Shores foi demonstrado em três configurações: uma com chiplets de CPU, uma com dois chiplets de CPU e dois chiplets de GPU, e uma com todos os chiplets de GPU — organização muito semelhante ao dos Xeon Sapphire Rapids, por contar com 4 chiplets, mas significativamente mais avançada. A promessa de flexibilidade sugere que mais configurações são possíveis de acordo com a necessidade da empresa que o utilizará.

Alguns dos destaques confirmados para o super acelerador incluem litografia da era Angstrom, sinalizando o uso do Intel 20A (~2 nm) ou Intel 18A (~1,8 nm), tecnologias avançadas de empacotamento, possivelmente relacionadas à adoção de uma nova geração das tecnologias de empilhamento 2,5D EMIB e 3D Foveros de chips da gigante, e I/O líder de indústria, que pode envolver os barramentos PCIe 6.0 e CXL.

Ainda segundo a empresa, em desempenho, todos os avanços tecnológicos e a combinação de CPU e GPU em um único soquete ofereceriam 5 vezes mais performance/Watt, 5 vezes mais densidade de computação em um único soquete x86 e 5 vezes mais capacidade e largura de banda de memória, números impressionantes considerando a previsão de estreia para 2024/2025.

Fora isso, um dos grandes trunfos do Falcon Shores, pensado para facilitar a transição para a arquitetura unificada, é o uso da OneAPI, o conjunto de soluções de software da empresa que permite realizar uma programação única para CPUs, GPUs e XPUs. A ambição da Intel com essa suíte de desenvolvimento é facilitar a vida dos programadores, já que o próprio código ficaria responsável por selecionar que parte do hardware deve executá-lo para obter os melhores resultados.

Xeon Sapphire Rapids com HBM ganha dados de desempenho

A conferência foi finalizada com a exbição de novos dados de desempenho dos processadores Sapphire Rapids com HBM, pertencentes à 4ª geração da família Intel Xeon Scalable. Como o nome da série de modelos sugere, o principal destaque dos componentes é a adição de até 64 GB de memória HBM2e no die, ao lado dos chiplets de processamento.

Essa memória atua como uma espécie de cache turbinado, reduzindo os acessos à RAM do sistema e melhorando drasticamente a performance em aplicações sensíveis à latência resultante desse processo.

Utilizando testes selecionados e comparando os resultados com a performance de um Xeon Platinum 8380, topo de linha da 3ª geração Xeon Scalable Ice Lake-SP, os chips Sapphire Rapids com HBM seriam mais de 3 vezes mais rápidos em processamento de áreas como energia e simulação de física, e mais de 2 vezes mais velozes em previsão do tempo e fabricação mecânica, todos sensíveis à latência.

Junto aos modelos tradicionais, a série Sapphire Rapids com HBM da família Xeon Scalable de 4ª geração está prevista para estrear oficialmente ainda neste ano, recebendo uma linha sucessora, a Emerald Rapids, em 2023.