UCIe: Intel se une a AMD e TSMC em padrão de design aberto de chiplets

Por Renan da Silva Dores • Editado por Wallace Moté |

Em comunicado divulgado nesta quarta-feira (2), a Intel anunciou uma parceria com AMD, Qualcomm e outras gigantes do mundo da tecnologia para o estabelecimento de um consórcio para o desenvolvimento do Universal Chiplet Interconnect Express (UCIe), padrão aberto para comunicação entre chiplets dentro de processadores baseados no design de Multi-Chip Module (MCM). A novidade visa criar um ecossistema na indústria, e "possibilitar a inovação em diferentes segmentos do mercado".

- O que é aceleração de hardware e quando usar

- Intel NUC 12 Extreme traz chips Alder Lake de desktop e GPUs de até 350 W

Intel, AMD e Qualcomm se unem em design aberto de chiplets

Segundo a Intel, o UCIe foi desenvolvido com base no Advanced Interface Bus (AIB) e doado ao grupo de empresas integrantes do consórcio, que conta ainda com ARM, Google, Meta (Facebook), Microsoft, Samsung e TSMC. Resumidamente, a nova interface estabelece requisitos de hardware e software para permitir a comunicação de chiplets fabricados por diferentes empresas, e deve ser similar a outros padrões abertos da indústria, como o USB e o barramento PCIe, do qual parece ter se inspirado no nome.

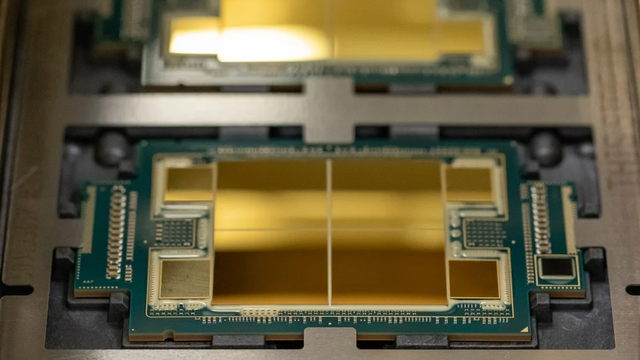

Os chips baseados no design MCM são, basicamente, soluções compostas por chips menores, comumente conhecidos como chiplets. Esse formato não apenas reduz os custos, já que chips menores costumam ter melhor rendimento durante a fabricação, aumentando assim a quantidade produzida em um mesmo wafer de silício, como também é considerado o caminho para manter viva a Lei de Moore, que estabelece um aumento de 100% na contagem de transistores a cada 2 anos.

Para que o design funcione de maneira apropriada, uma interface de alta velocidade precisa ser inserida no substrato do chip, permitindo que os chiplets se comuniquem com a menor latência possível e evitando perdas de desempenho. Diferentes empresas, como a TSMC e a própria Intel, acabaram desenvolvendo soluções proprietárias para esse problema.

O UCIe quer expandir as possibilidades ao estabelecer uma interface única para todas as fabricantes de semicondutores, o que agilizaria o processo de produção de novos processadores e permitiria a comunicação entre chiplets fabricados por diferentes fundições. O resultado seria semelhante ao que a Intel pretende implementar com a GPU para data centers Ponte Vecchio e as CPUs Meteor Lake de 14ª geração, que combinam chiplets da própria companhia com os fabricados pela TSMC.

UCIe será incorporado a partir do fim de 2022

A nova interface aberta funciona em camadas, trazendo uma física, responsável pelos sinais elétricos, clock e outros aspectos, e um adaptador de die para die, encarregado de gerenciar os estados da conexão e a negociação dos parâmetros da comunicação entre chiplets. O padrão pode ser aplicado no empacotamento tradicional, diretamente no substrato do chip, ou ainda em tecnologias como a EMIB da Intel e a CoWoS da TSMC, de empilhamento 2,5D.

Apesar de não serem compatíveis no momento, tecnologias de empacotamento 3D, como a Intel Foveros e soluções da família 3DFabric da TSMC, serão suportadas no futuro. A última camada, de software, segue a proposta aberta e visa facilitar a adoção, realizando toda a comunicação utilizando os protocolos PCIe e CXL, por já serem amplamente adotados no mercado.

A versão inicial do protocolo atenderá a dois formatos: a comunicação tradicional entre chiplets, presentes desde o segmento de portáteis até servidores de alto desempenho, e UCIe Retimers, que permitirão a comunicação de alta velocidade entre racks de servidores ou mesmo pods inteiros. Para garantir o máximo possível de interoperabilidade, o padrão suportará diferentes taxas de transferência de dados, densidade de interposers e alcance de canais.

Ainda é cedo para garantir que o UCIe será de fato amplamente adotado pela indústria, especialmente frente a rivais como o Bunch of Wires (BoW), solução similar, apesar de menos flexível e customizável, desenvolvida por outro consórcio mais amplo, o Open Compute Project (OCP), que inclui nomes de peso ausentes no novo grupo como Nvidia e IBM.

Mesmo assim, a presença de três das maiores fundições do mundo (Intel, Samsung e TSMC) já indica um bom começo. O comunicado afirma que os membros fundadores do consórcio terminarão a implementação do UCIe 1.0 no final de 2022, começando logo em seguida o desenvolvimento da segunda geração da interface.