Intel e ARM trabalham para otimizar núcleos de celular em 1,8 nm

Por Renan da Silva Dores • Editado por Wallace Moté |

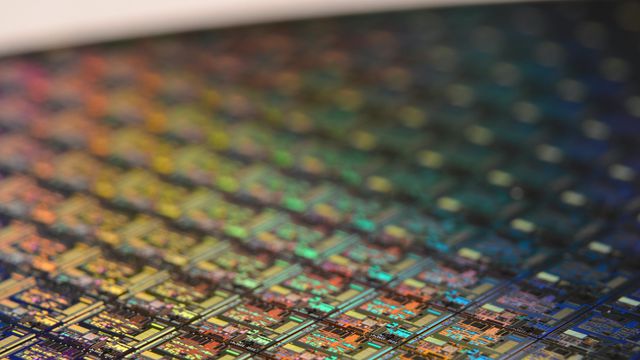

Em comunicado divulgado nesta quarta-feira, a Intel Foundry Services (IFS) — divisão da gigante responsável pela fabricação de chips — anunciou que está trabalhando com a ARM para otimizar futuros núcleos de chips de celular para a litografia Intel 18A, equivalente à classe de 1,8 nm. A novidade não é importante apenas para a IFS, que dá mais um passo para se tornar uma forte concorrente da TSMC, como também sugere que devemos ver processadores de smartphones de marcas como a Qualcomm utilizar tecnologia da Intel em breve.

- Intel confirma linha Meteor Lake como sua 14ª geração de processadores

- Ampere lança kit que une CPU ARM e suporte a Windows e GPUs Nvidia

Segundo as informações, o acordo de colaboração entre as gigantes se estenderá por várias gerações, mirando inicialmente na litografia Intel 18A, equivalente a 1,8 nm, prevista para entrar em fase de produção em massa no final de 2024. O aspecto mais interessante é que o trabalho conjunto desenvolverá otimizações primeiro para designs de chips para smartphones, ainda que esteja nos planos expandir a cooperação para projetos de processadores para veículos, Internet das Coisas (IoT), data centers e outras aplicações.

A colaboração é bastante profunda, e envolve a chamada Co-otimização de Tecnologia de Design (DTCO), em que o design dos chips e o processo de fabricação são otimizados juntos para garantir melhores consumo, performance, área e custo, métrica conhecida na indústria como PPAC, especificamente para os núcleos da ARM. Com a parceria, Intel, ARM e as empresas que projetam chipsets, como Qualcomm e MediaTek, também otimizarão o software e novos formatos de empacotamento, como os cada vez mais populares chiplets.

Parte da estratégia IDM 2.0, em que a Intel Foundry Services se tornou mais independente e se organizou para começar a fabricar componentes de outras empresas, a iniciativa é de enorme importância para garantir que as soluções dos clientes da IFS atinjam os resultados esperados com as litografias da gigante. Mais do que isso, o contrato é um grande reforço para que o time azul consiga se tornar uma opção competitiva e, possivelmente, até superior tecnologicamente falando em comparação à TSMC, sua principal rival e atual líder de fabricação de chips.

É interessante lembrar que as citadas Qualcomm e MediaTek já possuem contratos de fabricação com a Intel: a dona da família Snapdragon havia anunciado um acordo misterioso em que utilizaria exatamente a litografia Intel 18A para um futuro chipset, enquanto a concorrente taiwanesa responsável pela linha Dimensity iniciou a fabricação de chips em 22 nm, mas poderia acabar estreitando relações no futuro, especialmente após o tratado de cooperação entre IFS e ARM.

Considerando a janela de estreia do processo de fabricação, ainda deve demorar um pouco para termos novidades a respeito da colaboração. Mesmo assim, o futuro é promissor, se observarmos as promessas da Intel 18A: segunda litografia da "Era Angstrom" da Intel, a solução combina duas tecnologias de ponta para entregar supostos saltos massivos em desempenho e eficiência — os transistores RibbonFET e a PowerVia.

Já usados pela Samsung em sua litografia de 3 nm, e cotados para se tornarem o próximo padrão da indústria, os RibbonFET redesenham o formato dos transistores e os fazem ter contato com os portões de comunicação por todos os lados, em vez de apenas três, como é o caso dos atuais FinFET. Essa característica também reduz interferências e possibilita o aumento ou redução de sua largura, otimizando-os para entregarem mais desempenho ou menor consumo.

A PowerVia, por sua vez, busca solucionar um problema que deve crescer conforme as litografias ficam cada vez menores: os componentes de hoje em dia são alimentados por nanofios construídos juntos dos circuitos de processamento, o que, nas litografias menores, resultam em interferência nos dados processados. A tecnologia da Intel vai realinhar esses fios para alimentar o chip pela parte traseira, em vias que atravessam o circuito, reduzindo as interferências e até mesmo aumentando a eficiência.

Fonte: Intel