AMD detalha tecnologia dos novos chips Ryzen 5000 com 3D V-Cache

Por Renan da Silva Dores | Editado por Wallace Moté | 24 de Agosto de 2021 às 09h36

A AMD surpreendeu quando anunciou em junho deste ano o 3D V-Cache, tecnologia pela qual passará a empilhar chips de memória sobre os processadores da marca. Segundo a fabricante, a novidade aumenta significativamente a densidade do CPU e pode chegar a triplicar a quantidade de cache aplicado em um único processador.

- Radeon RX 6600 "emulada" indica desempenho de possível nova placa da AMD

- CPUs AMD Threadripper 5000 "Chagall" voltam a vazar com 64 núcleos e até 280 W

Previsto para estrear oficialmente ainda neste ano, a empresa aproveitou a realização da feira HotChips 33 nesta semana para revelar novos detalhes do 3D V-Cache, os recursos utilizados para conseguir alcançar a elevada densidade e o que está sendo estudado e desenvolvido no momento para contornar os limites da Lei de Moore.

3D V-Cache entrega alta densidade e eficiência

É importante lembrar que a técnica de empilhamento não é exatamente nova — a Intel trouxe a tecnologia ao mercado primeiro com a Foveros, utilizada nos agora encerrados Intel Lakefield. No entanto, os métodos utilizados pela AMD com o 3D V-Cache prometem avanços substanciais frente à concorrência, aprimorando de maneira significativa a performance, o consumo, a área e o custo, métricas conhecidas em inglês como PPAC.

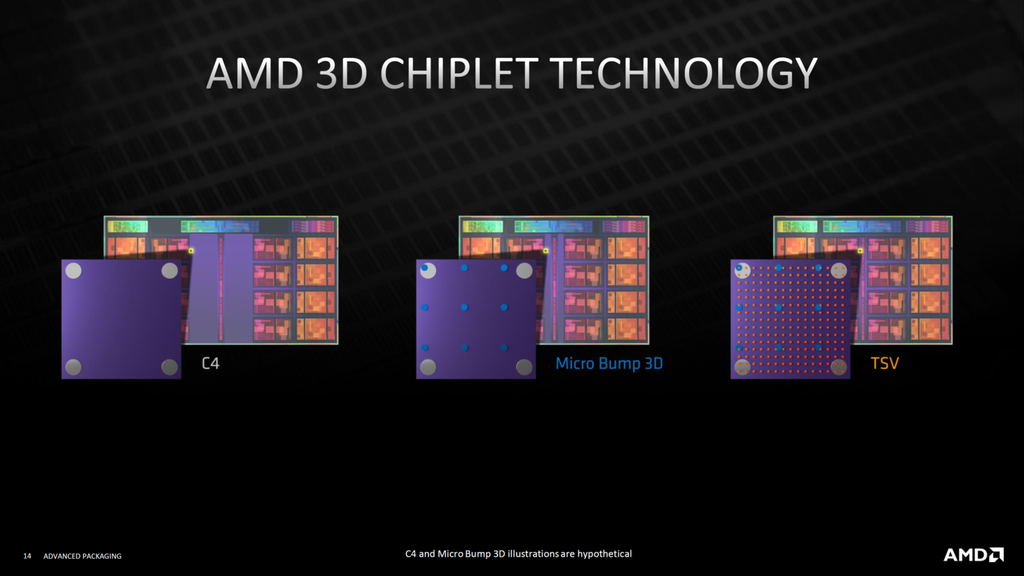

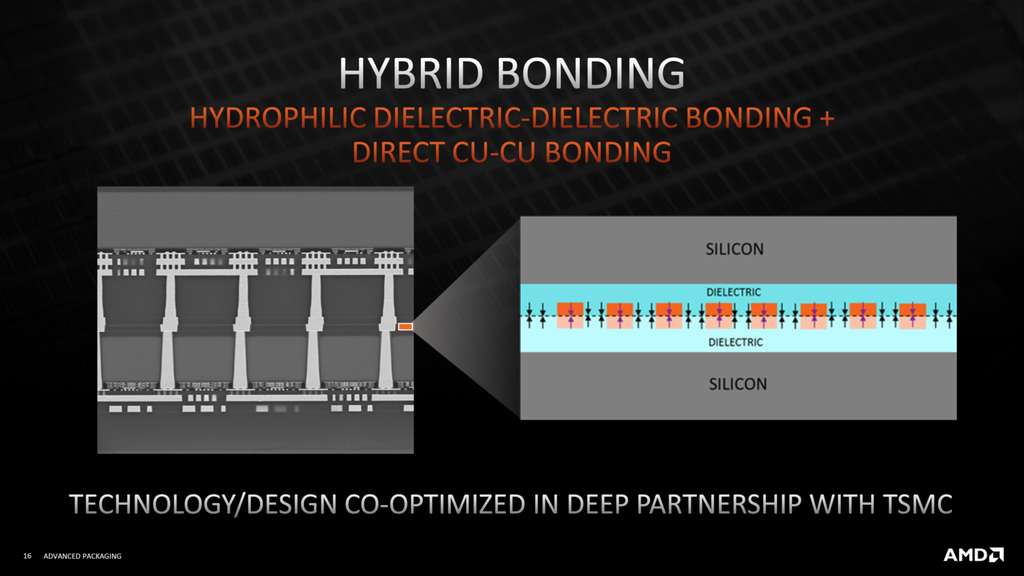

A imagem acima exemplifica exatamente como a tecnologia da AMD é mais avançada ao mostrar a densidade atingida pelo 3D V-Cache, no caso a quantidade de interconexões aplicadas nos chips. O segredo está na maneira pela qual as conexões são feitas: enquanto a Foveros utiliza o método de Micro Bump 3D, uma espécie de solda microscópica, a solução do time vermelho emprega um novo método mais complexo, desenvolvido junto à TSMC.

A fixação ocorre em duas fases: a primeira realiza a ligação dos dielétricos dos dois chips em um processo hidrofílico a temperatura ambiente, seguido de um recozimento, que reduz a dureza do material para estabelecer as conexões. A segunda fase liga então os conectores de cobre das vias de silício (Through Silicon Vias, TSVs) com a difusão de estado sólido, que integra os materiais com aquecimento.

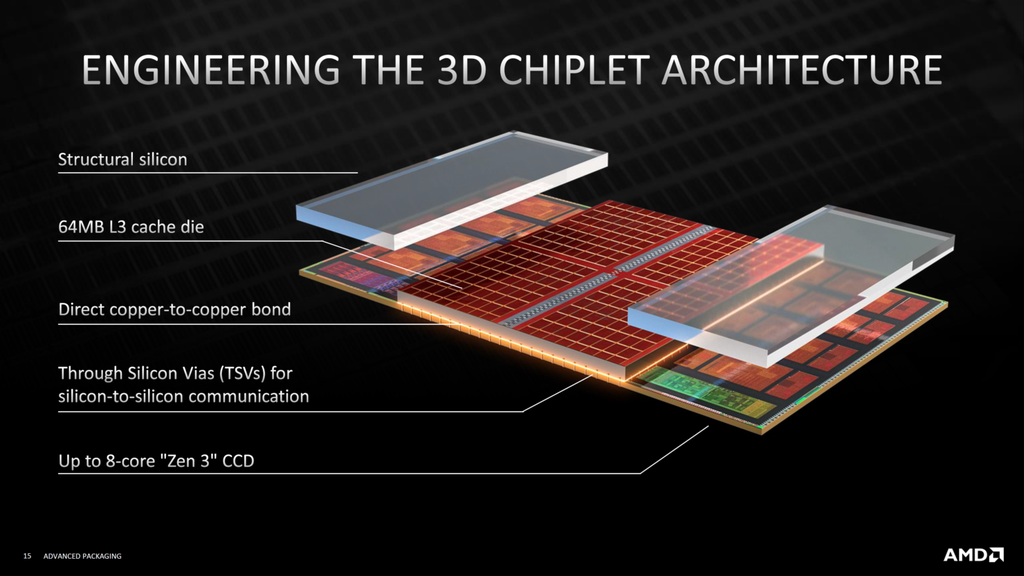

O novo chip de memória é colocado logo acima do cache L3, para se manter afastado do calor gerado pelos núcleos da CPU, e há ainda a adição de uma camada de silício estrutural no restante da superfície do processador para nivelá-lo e assim facilitar o resfriamento. Segundo a AMD, os processos e os TSVs são similares aos de chips tradicionais, o que facilita a fabricação e permite que o rendimento seja alto.

Com o 3D V-Cache, a fabricante promete manter a latência baixa, graças à largura de banda de 2 TB/s entre os chips, consumir 3 vezes menos que outros métodos de empilhamento e entregar densidade 15 vezes maior — o TSV Pitch, a distância entre cada uma das vias de silício, é de apenas 9 micrômetros, contra 50 micrômetros do Micro Bump 3D utilizado nos processadores Intel Lakefield, que serviram de base para os números da AMD.

Outra enorme vantagem sobre a Intel está justamente no prazo de lançamento: os primeiros processadores Ryzen 5000 com 3D V-Cache entrarão na fase de produção em massa ainda neste ano, para chegar aos consumidores pouco depois. A única tecnologia equivalente do time azul, a Intel Foveros Direct, que promete um TSV Pitch de 10 micrômetros, estreia apenas em 2023.

Futuro do empilhamento de chips

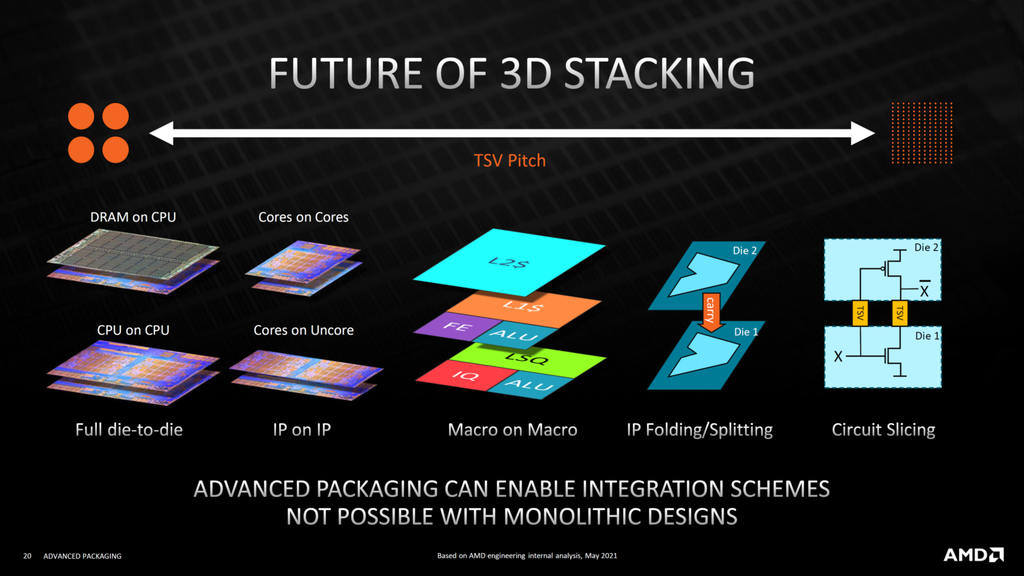

A AMD também revelou que segue estudando maneiras de expandir as tecnologias de empilhamento de chips, as quais estaria considerando ser o futuro da fabricação de semicondutores. Conforme ocorrerem avanços, poderemos ver aplicações mais amplas, com o empilhamento de RAM, CPUs ou ainda a separação dos circuitos em diferentes camadas.

Como lembra o site Tom's Hardware, os maiores desafios no momento são o aquecimento gerado pelos componentes, já que seria difícil resfriá-los de maneira otimizada estando empilhados, a alimentação, também dificultada pelo empilhamento, e os próprios processos de fabricação, que precisam ser eficientes para conseguir atingir as etapas de produção em massa.

Fonte: WCCFTech, TechSpot, Tom's Hardware