O que é a tecnologia Intel Foveros?

Por Felipe Vidal • Editado por Jones Oliveira |

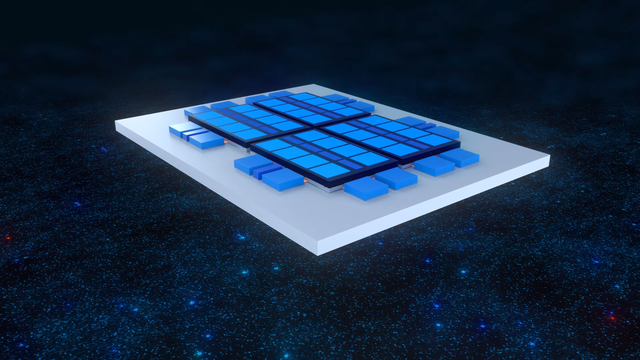

A Intel Foveros é uma tecnologia para realizar o empacotamento 3D de processadores. Basicamente, esse recurso permite que a fabricante empilhe diversos blocos em um chip, como a estrutura da placa de vídeo integrada, da CPU propriamente dita, memórias, etc.

- O que é AMD Ryzen Threadripper?

- Intel Core i3, i5 e i7: entenda a nomenclatura e qual deles é o ideal para você

Em outras palavras, a Foveros atua com tiles para formar uma "brincadeira de Lego", colocando uma peça por cima da outra. Isso cria vantagens no desenvolvimento, pois a chance de se fabricar chips defeituosos é menor e o custos financeiros para e empresa diminuem. Para explicar mais sobre a tecnologia Intel Foveros, o Canaltech conversou com Yuri Daglian, Engenheiro de Aplicações da Intel Brasil.

Chips monolíticos

Antes de entender o que é a tecnologia Intel Foveros de maneira mais aprofundada, é preciso conhecer um pouco da estrutura básica de um chip. O formato mais comum é chamado de empacotamento monolítico, pois utiliza um único bloco de silício. Nesse único bloco há todos os componentes unidos: a CPU, os núcleos, memórias, cache, I/O e assim por diante. O formato monolítico faz com que todo o tráfego de informações flua facilmente e tenha uma performance bem alta.

Porém, com o avanço da tecnologia, o sistema monolítico começou a ficar inviável. De acordo com a Lei de Moore, a quantidade de transistores presentes em um chip dobra a cada dois anos e para que isso continue acontecendo, as empresas precisam de blocos de silício cada vez maiores. Quanto maior o bloco, maiores as chances de o produto sair defeituoso da fábrica. Outro problema está relacionado com o maquinário utilizado, pois para aumentar a densidade de transistores no bloco através da litografia, as máquinas de produção ficam cada vez mais caras.

"Se eu sigo esse modelo de fabricação de chips monolíticos ficando cada vez mais complexos, com a litografia ficando cada vez mais avançada e mais cara de ser utilizada, em algum momento vai ser inviável de produzir processadores. Eles vão ficar caros demais e não será possível produtizar isso", comenta Yuri Daglian.

Empacotamento desagregado via tiles

Para contornar esse problema, a indústria criou o conceito de empacotamento via chiplets ou tiles, nomes adotados por empresas diferentes, mas que são a mesma coisa. Nesse conceito inicial, o empacotamento, ou seja, a forma como o processador é montado, é feito de maneira 2D através de vários chips menores.

É como se aquele bloco único de silício fosse desmontado e os tiles representassem um pedaço de cada componente. Um chip 2D tem um tile separado para a CPU, um pedaço da iGPU, uma parte para memórias, outra para cache, I/O e assim sucessivamente. É como se você montasse um quebra-cabeça para criar uma imagem.

Nessa analogia, as peças do quebra-cabeça são os tiles, enquanto a base onde você monta o jogo é chamada de base tile ou interposer. Dividir o chip em diversos bloquinhos alivia os custos na produção e minimiza erros, pois caso um tile de memória fique ruim no desenvolvimento, basta que os engenheiros substituam esse tile por um novo, sem a necessidade de descartar todo o chip, como acontece no formato monolítico.

Também há uma questão forte a respeito da litografia. Fabricar em tiles permite que o base tile seja feito em 22nm, pois não comprometeria a performance. O mesmo pode servir para o tile de I/O, feito em 12nm, que também não afeta o desempenho. Por outro lado, o tile de computação e iGPU já podem ser feitos em uma litografia de 7nm, priorizando performance e mais eficiência energética. Assim, a fabricante monta o chip com mais desempenho e menos custos na produção.

No fim das contas, a fabricação em 2D permite que as empresas tenham autonomia para montar seu processador com diferentes litografia. Quanto menor é a litografia, maiores são os custos. Logo, criar um processador "misto" pode ser muito atraente do ponto de vista financeiro.

"O próprie tile de GPU não é fabricado na Intel. É feito em uma fábrica externa. Então em uma geração futura eu poderia manter o SoC de I/O se ele não tiver alterações muito grandes, e posso incrementar um novo tile de GPU, caso hajam muitos avanços nessa área", revela Yuri. Isso cria também uma maior versatilidade e escalabilidade para o futuro, já que a companhia pode melhorar os produtos ao adicionar novos blocos melhorados.

Entendendo o que é EMIB

Para que a Intel pudesse fazer isso de forma apropriada, o time azul criou uma tecnologia chamada EMIB (embedded multi-die interconnect bridge), que pode ser definida como uma ponte que conecta os tiles. A EMIB é uma pecinha minúscula, que fica abaixo dos tiles para encaixar todas essas pequenos chips entre si e garantir o seu funcionamento.

"O EMIB é basicamente uma ponte de cobre que conecta todos os tiles para que eles se comuniquem de forma adequada. Mas vale salientar que essa ponte atua no plano 2D, ou seja, os tiles são conectados uns com os outros no plano horizontal, lateralmente, como uma espécie de costura", salienta o engenheiro.

Entendendo o que é a Intel Foveros

Para que tudo isso funcionasse corretamente, a Intel precisou desenvolver e aprimorar a tecnologia Foveros. Esse recurso existe desde 2019, na geração Lakefield, mas só recentemente ganhou notoriedade, já que a segunda geração será implementada nos processadores Meteor Lake. A Foveros é o recurso que permite o empilhamento vertical dos chipsets, por isso é chamado de empacotamento 3D.

De maneira simplificada, a Foveros é o que permite os chiplets ficarem sobrepostos no interposer, garantindo conectividade, velocidade na transmissão de dados, alta largura de banda e baixa latência. Em outras palavras, a Intel Foveros é o que permite colocar um tile por cima do outro, além da conexão lateral com a EMIB.

Como a Foveros funciona?

Ao olhar as imagens abaixo, é possível entender que a Foveros são esses minúsculos pilares de cobre (Cu) e níquel (Ni) que sustentam os tiles. É como se fosse a construção de uma obra de engenharia, e essas estruturas representassem os pilares que seguram a construção. Esses pilares são chamados de TSVs (Vias através do Silício) e servem para transportar energia verticalmente, mas também desempenham esse papel mecânico de "segurar" os tiles.

No entanto, as TSVs não são inseridas no meio dos tiles, pois lá ficam os circuitos dos chips e isso destruiria o projeto. Por isso, esses pilares estão restritos às bordas dos tiles, algo que deve mudar nas gerações futuras da tecnologia Intel Foveros. Aliás, o empilhamento vertical pode ter um impacto na altura final dos processadores, na casa de 1 ou 2mm. Segundo Yuri esse valor é baixo, mas poderia inviabilizar a instalações de certos coolers.

Vale mencionar que, obrigatoriamente, a segunda geração da Foveros faz com que o base tile necessite ser fisicamente maior do que os tiles superiores. Isso acontece, pois é a única forma atual de passar as TSVs pelas bordas. Caso o base tile fosse menor, essas vias entre o chips passariam pelo meio dos tiles e os destruiriam.

Desvantagens da Intel Foveros

Porém, há algumas desvantagens e empicilhos técnicos relacionados à Intel Foveros. Yuri explica que esse empilhamento acaba servindo como “cobertores”. Basta pensar que o chip é uma espécie de cama, com o base tile servindo de colchão e os tiles restantes são empilhados como cobertores. Isso faz com que haja muito calor envolvido, e consequentemente menos performance.

Isso também gera discussões sobre como os sinais elétricos serão transportados entres os tiles. Por exemplo, como seria para levar os dados do GPU Tile para o tile de I/O? Esses dados passariam pelo tile de SoC que fica entre ambos, ou os sinais elétricos seriam transportados por baixo, pelas pontes de EMIB?

Daglian comenta que isso depende muito do projeto, já que a energia e/ou os dados podem passar de tile em tile até chegarem a um chip específico, ou podem ser movidos por baixo, até chegar ao destino final. No entanto, o engenheiro destaca que o EMIB é mais viável para tiles lado a lado do que os muito distantes, mas não há uma explicação correta para esse tipo de questionamento.

Próximas gerações da Foveros

Para contornar esses e outros problemas, as próximas gerações da tecnologia Foveros devem trazer incrementos muito significativos. No entanto, as novas versões ainda estão em estudo e não têm data para serem implementadas em novos processadores.

Foveros Omni

A terceira geração, chamada de Foveros Omni, pretende fazer com que o base tile/interposer também seja desagragregado, ou seja, separado em várias pequenas partes. Isso possibilitará que as TSVs sejam colocadas no meio chips, sem que haja danos nos circuitos. Isso deve resolver o problema de por onde a energia seria transmitida para os tiles, já que as colunas não ficariam mais nas bordas, de acordo com a explicação de Yuri.

Além disso, como a imagem abaixo mostra, a Omni também possibilitaria que os tiles superiores fossem maior que os base tiles. Nesses casos, as colunas de cobre sairiam do substrato (o chão do processador) até o tile mais alto. A distância entre os base tiles e os tiles também diminuiria para 25 micrômetros, uma redução de 50% em relação à segunda geração.

Foveros Direct

A Foveros Direct seria a maior revolução no sistema de empacotamento desagregado da Intel. Em resumo, a ideia é retirar as colunas de TSV, pois os tiles estariam praticamente "colados" uns aos outros através de estruturas com uma distância minúscula de até 10 micrômetros. Isso permitiria mais resistência e eficiência energética melhorada, além de possibilitar que mais tiles fossem empilhados.

"Basicamente é feito um contato quase que inteiro entre os tiles, mas com pequenos ajustes [...] Se eu tenho uma tecnologia como a Foveros Direct, que a conectividade entre os dois tiles é praticamente total, ou seja, sem depender daqueles pilares, a largura de banda é muito maior e eu consigo ter muito mais performance. É como se o tile de cima fosse transparente e não vai mais haver perda de energia. Quando chegarmos na Foveros Direct, imagine que vamos ter um lego para fazer processadores como quisermos", ressalta Daglian.

Foveros para todos?

Na conversa do Canaltech com o engeheiro da Intel, Yuri destacou que a tecnologia Foveros poderá ser utilizada por outras empresas mediante vendas e licenciamento, já que é uma propriedade intelectual da Intel. Isso deve acarretar em grandes benefícios para o desenvolvimento das próximas gerações de processadores para PCs e até outras soluções de hardware.

Afinal, o que é a Intel Foveros?

A tecnologia Intel Foveros não é somente uma técnica ou processo, mas sim um conjunto de elementos. É preciso entender esse recurso como uma forma de empilhamento de chips menores sob um chip base, que fica apoiado no substrato da CPU. A Foveros é uma forma para empilhar tiles, mas quando combinada com a EMIB, se torna uma técnica de empacotamento de chips.

“O EMIB permite uma conectividade 2D no plano. A Foveros permite a conectividade 3D. Então eu consigo colocar, literalmente, um chip em cima do outro, e consigo fazer com que esses dois se comuniquem", finaliza Yuri Daglian.