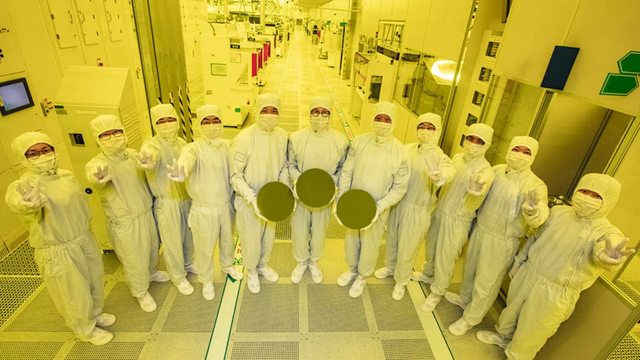

Samsung rebatiza 2ª geração de wafers em 3 nm para 2 nm

Por Daniel Trefilio • Editado por Jones Oliveira |

Samsung causa polêmica ao rebatizar 2ª geração de wafers fabricados em 3 nm para 2 nm para se posicionar de forma competitiva em relação ao processo Intel 20A, equivalente a 2 nm. A iniciativa levanta questionamentos sobre como vem sendo feita a comunicação oficial sobre a fabricação wafers de silício, uma vez que medida, de fato, não está relacionada ao tamanho “real” dos semicondutores.

Os termos 5 nm, 3 nm, 2 nm, e assim por diante, são utilizados deliberadamente pelas fabricantes de chips para representar a densidade de transistores em dies de silício, e não o tamanho efetivo dos componentes. Na prática, cada componente de um chip tem tamanhos diferentes e esses números são apenas marcas para facilitar a compreensão dos produtos.

Nem os chips em 3 nm têm 3 nm

O processo de redução de litografias é bem mais complexo do que apenas imprimir circuitos e transistores cada vez menores, passando por mudanças profundas nas estruturas desses componentes. Por essa razão, a nomenclatura de litografia em nanômetros é uma medida relativa de densidade, que envolve o formato dos portões lógicos dos circuitos e empacotamento 3D, para acomodar mais componentes por área da PCB.

Por essa razão, o rebranding da Samsung para seu processo de fabricação de 3 nm de 2ª geração para 2 nm não, necessariamente, uma propaganda enganosa ou golpe publicitário. Ao que tudo indica, a medida da sul-coreana visa reposicionar seu processo de fabricação em relação aos chips da Intel.

Os processos de fabricação Intel 4 e Intel 20A também não são, de fato, em 4 nm e 2 nm respectivamente, no entanto, a comunicação da empresa é mais clara ao sempre combinar “Intel 20, equivalente a 2 nanômetros” em seus materiais oficiais.