Samsung e TSMC estão com dificuldades para fazer chips de 3nm

Por Daniel Trefilio • Editado por Jones Oliveira |

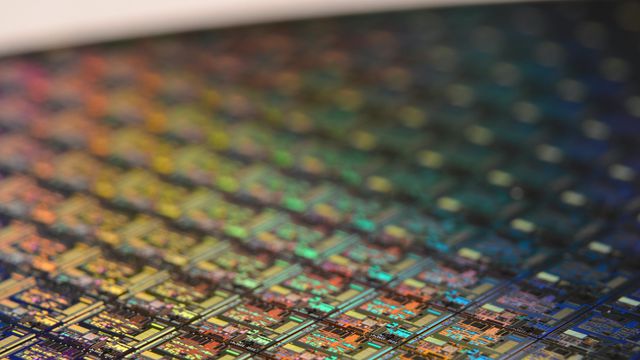

Wafers de silício para chips em 3nm da Samsung e TSMC ainda estão apresentando rendimentos de 60% e 50%, respectivamente. Isso significa que ambas as companhias estão enfrentando dificuldades e que pouco mais da metade dos chips produzidos em cada wafer é, efetivamente aproveitável para o mercado.

- GPUs Nvidia Blackwell GB100 utilizarão litografia de 3nm da TSMC

- Chips de IA da TSMC devem ficar mais caros em breve

Ao que tudo indica, o processo GAA FET (Gates-All-Around), já adotado pela Samsung, é um pouco mais eficiente que o FinFET da TSMC. Supostamente, a gigante chinesa estaria com dificuldades para migrar para o GAA FET, inclusive atrasando o início da produção em 2nm, dando margem para a Intel crescer no mercado.

Impacto em grandes contratos

Segundo os relatórios divulgados pelo veículo sul-coreano ChosunBiz, os números de rendimento são apenas 5% a 10% melhores do que os apresentados no final do segundo trimestre de 2023. Para serem considerados viáveis para fabricação em larga escala, os wafers de silício precisam apresentar rendimentos acima de 70%.

Nos patamares atuais, a produção em massa ainda não é comercialmente viável a ponto de atrair grandes contratos. Isso não apenas pode atrasar a produção em massa dos novos chips, como também pode impactar contratos já firmadas para a tecnologia.

Atualmente, a Apple é uma das maiores clientes da TSMC para chips de litografia de 3nm, utilizado nos processadores A17 Pro, dos novos iPhone 15 Pro e Pro Max. Em paralelo, as novas GPUs Blackwell da Nvidia contam com a mesma litografia e estão previstas para chegar ao mercado de servidores para IA já em 2024.

Caso o baixo rendimento afete, de fato, a produção em massa da TSMC, isto pode se refletir, também, na capacidade da Nvidia de atender seus próprios contratos para as GPUs GB100 voltadas para IA e HPC.